# Advanced x86:

# BIOS and System Management Mode Internals SPI Flash Protection Mechanisms

# Xeno Kovah && Corey Kallenberg LegbaCore, LLC

### All materials are licensed under a Creative Commons "Share Alike" license. http://creativecommons.org/licenses/by-sa/3.0/

You are free:

to Share — to copy, distribute and transmit the work

to Remix - to adapt the work

#### Under the following conditions:

Attribution — You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

Share Alike — If you alter, transform, or build upon this work, you may distribute the resulting work only under the same, similar or a compatible license.

Attribution condition: You must indicate that derivative work

"Is derived from John Butterworth & Xeno Kovah's 'Advanced Intel x86: BIOS and SMM' class posted at http://opensecuritytraining.info/IntroBIOS.html" 2

# How to stop someone from writing to your BIOS

- AKA "How to stop an attacker from writing to your BIOS"

- AKA "What the BIOS vendors are typically configuring wrong when they're supposed to be stopping attackers from writing to your BIOS"

### **Flash Protection**

| Mechanism                         | Accesses<br>Blocked | Range<br>Specific? | Reset-Override<br>or SMI#-<br>Override? | Equivalent Function on<br>FWH                     |

|-----------------------------------|---------------------|--------------------|-----------------------------------------|---------------------------------------------------|

| BIOS Range<br>Write<br>Protection | Writes              | Yes                | Reset Override                          | FWH Sector Protection                             |

| Write Protect                     | Writes              | No                 | SMI# Override                           | Same as Write Protect in<br>previous ICHs for FWH |

#### Table 5-60. Flash Protection Mechanism Summary

- With no Flash Descriptor present, the only mechanisms to lock the flash are:

- BIOS Range Write Protection

- Global Flash Write Protection

- The reference to FWH Sector Protection yields no results in any datasheets. I am assuming it is related to the R/W control shown in the sample FWH register map at the beginning of the BIOS Flash section

# Flash Protection Mechanism #1

#### Table 5-60. Flash Protection Mechanism Summary

|   | Mechanism                         | Accesses<br>Blocked | Range<br>Specific? | Reset-Override<br>or SMI#-<br>Override? | Equivalent Function on<br>FWH                     |

|---|-----------------------------------|---------------------|--------------------|-----------------------------------------|---------------------------------------------------|

|   | BIOS Range<br>Write<br>Protection | Writes              | Yes                | Reset Override                          | FWH Sector Protection                             |

|   | FIOLECCION                        |                     |                    |                                         |                                                   |

| 4 | Write Protect                     | Writes              | No                 | SMI# Override                           | Same as Write Protect in<br>previous ICHs for FWH |

- Covering this first because I believe it to be your first line of defense to protect your BIOS flash from writes

- Applies to the <u>entire</u> flash chip (Global Flash Protection)

- Provides SMM the ability to determine whether or not a request to unlock the BIOS flash for writing will be permitted

- This protection is provided by the chipset (not on the flash itself)

# **Global BIOS Write Protection**

#### BIOS\_CNTL—BIOS Control Register (LPC I/F—D31:F0)

| Offset Address: | DCh | Attribute:  | R/WLO, R/W, RO |

|-----------------|-----|-------------|----------------|

| Default Value:  | 00h | Size:       | 8 bit          |

| Lockable:       | No  | Power Well: | Core           |

| Bit |                                                                                                                                                  | Description                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 7:5 | Reserved                                                                                                                                         |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 4   |                                                                                                                                                  | Top Swap Status (TSS) — RO. This bit provides a read-only path to view the state of the Top Swap bit that is at offset 3414h, bit 0.         SPI Read Configuration (SRC) — R/W. This 2-bit field controls two policies related to BIOS reads on the SPI interface: |  |  |  |  |  |  |  |  |

|     |                                                                                                                                                  |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|     | Bit 3- Prefetch                                                                                                                                  | n Enable                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|     | Bit 2- Cache [                                                                                                                                   | Disable                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|     | Settings are s                                                                                                                                   | ummarized below:                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|     | Bits 3:2                                                                                                                                         | Description                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| 3:2 | 00b                                                                                                                                              | No prefetching, but caching enabled. 64B demand reads load<br>the read buffer cache with "valid" data, allowing repeated code<br>fetches to the same line to complete quickly                                                                                       |  |  |  |  |  |  |  |  |

|     | No prefetching and no caching. One-to-one correspondence of<br>host BIOS reads to SPI cycles. This value can be used to invalidate<br>the cache. |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|     | 10b <b>Prefetching and Caching enabled.</b> This mode is used for long sequences of short reads to consecutive addresses (i.e., shadowing)       |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|     | 11b                                                                                                                                              | Reserved. This is an invalid configuration, caching must be<br>enabled when prefetching is enabled.                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|     | BIOS Lock E                                                                                                                                      | nable (BLE) — R/WLO.                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 1   | 0 = Setting th                                                                                                                                   | e BIOSWE will not cause SMIs.                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 1   |                                                                                                                                                  | etting the BIOSWE bit to cause SMIs. Once set, this bit can only be<br>y a PLTRST#                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|     | BIOS Write I                                                                                                                                     | Enable (BIOSWE) — R/W.                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 0   | 1 = Access to<br>written fro                                                                                                                     | l cycles result in Firmware Hub I/F cycles.<br>the BIOS space is enabled for both read and write cycles. When this bit is<br>om a 0 to a 1 and BIOS Lock Enable (BLE) is also set, an SMI# is<br>d. This ensures that only SMI code can update BIOS.                |  |  |  |  |  |  |  |  |

- On MCH/ICH systems, bits 7:5 of the BIOS\_CNTL are reserved

- On this system BIOS\_CNTL is located in the LPC device (D31:F0, offset DCh)

- These protections would also apply to the Firmware Hub (FWH) if the BIOS were located there.

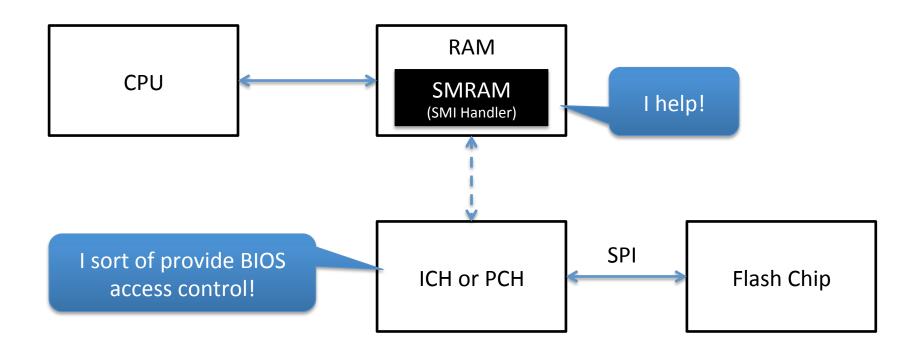

# ICH/PCH Chipset SMM-derived Write Protection:

|   | BIOS Lock Enable (BLE) — R/WLO.                                                                                                                                                                                                                                                                                      |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | <ul> <li>0 = Setting the BIOSWE will not cause SMIs.</li> <li>1 = Enables setting the BIOSWE bit to cause SMIs. Once set, this bit can only be cleared by a PLTRST#</li> </ul>                                                                                                                                       |

|   | BIOS Write Enable (BIOSWE) — R/W.                                                                                                                                                                                                                                                                                    |

| 0 | <ul> <li>0 = Only read cycles result in Firmware Hub I/F cycles.</li> <li>1 = Access to the BIOS space is enabled for both read and write cycles. When this bit is written from a 0 to a 1 and BIOS Lock Enable (BLE) is also set, an SMI# is generated. This ensures that only SMI code can update BIOS.</li> </ul> |

BIOS\_CNTL.BIOSWE (bit 0) enables write access to the flash chip

– Always R/W

• BIOS\_CNTL.BLE (bit 1) provides an opportunity for the OEM to implement an SMI to protect the BIOSWE bit

# How you should think of BLE

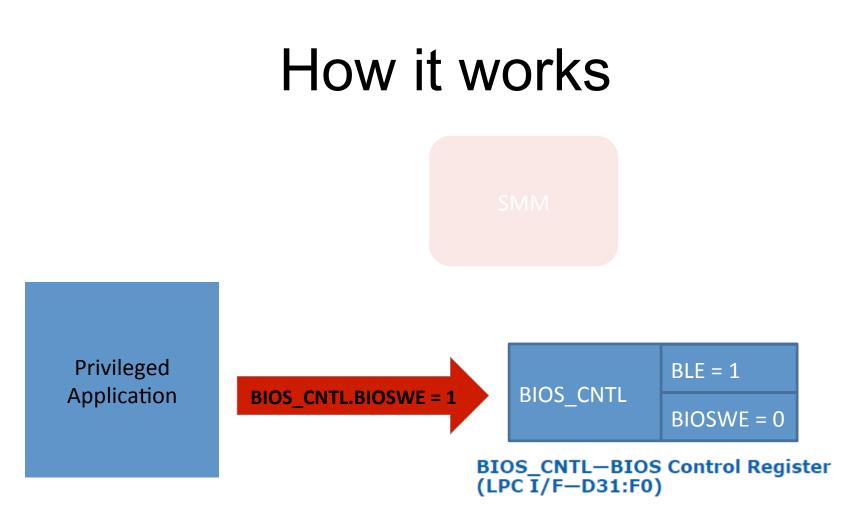

- Privileged app wants to write to the SPI flash, sets BIOS\_CNTL.BIOSWE to 1

- The only reason privileges are needed is to execute the in/out instructions

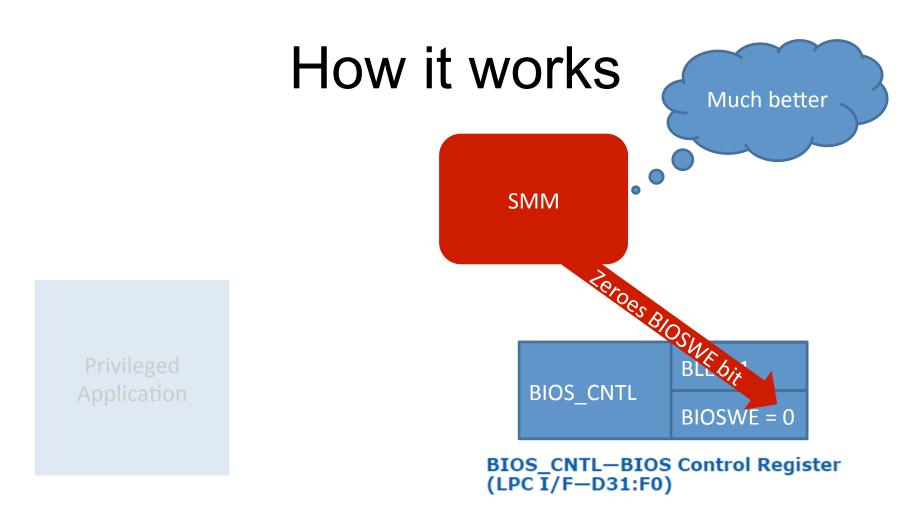

# How it works

- The BIOS\_CNTL register has the BIOS Lock (BLE) enabled

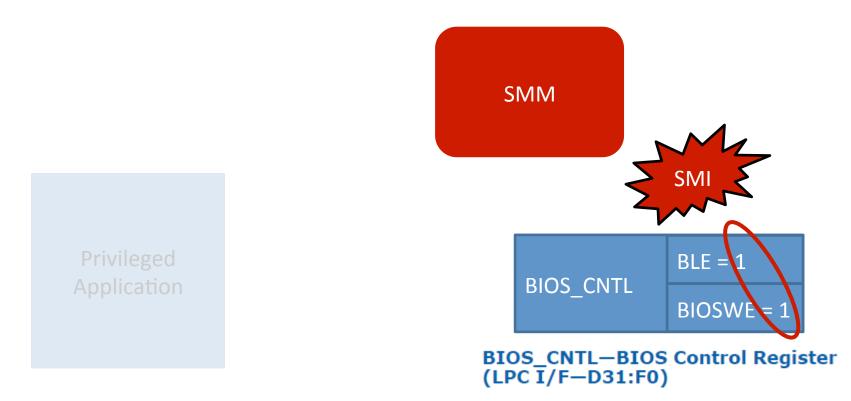

- Asserting BIOSWE while BLE is set generates an SMI#

- SMI# is initiated by the Chipset (ICH)

• The processor transitions to System Management Mode

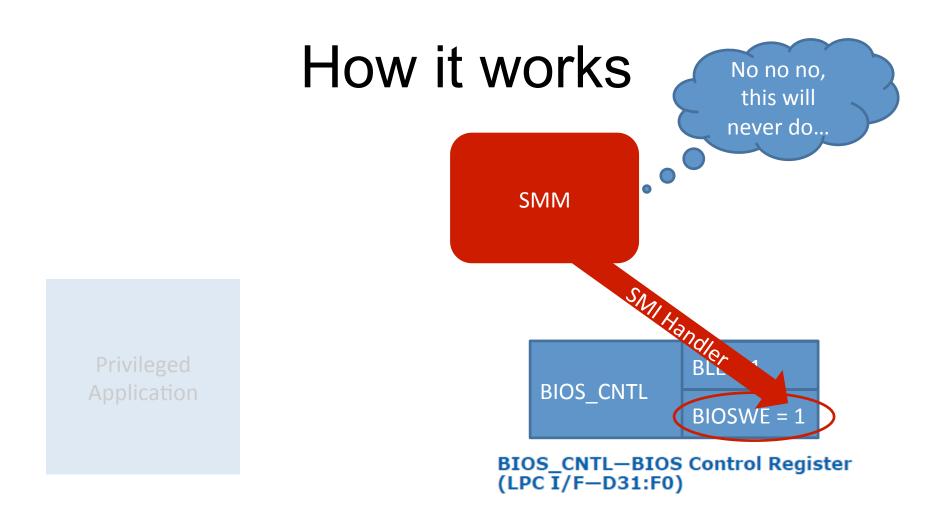

A routine in the SMI handler explicitly checks to see if BIOS\_CNTL.BIOSWE is set

- The SMI handler flips this bit back to 0, disabling writes to the serial flash

- Since updates should be applied only by SMRAM, SMRAM knows that unless it flipped this bit, this bit shouldn't be flipped.

- From the app's perspective, it appears the BIOSWE bit was never even asserted.

- Of course this only works if:

- BLE is asserted/enabled

- There is a SMI handler explicitly checking/resetting the BIOSWE bit

- SMIs cannot be somehow suppressed (you already saw 1 way)

### vulnBIOS example: BIOS\_CNTL Testing

| 📙 RW   | - Rea   | ad & \ | <b>Vrite</b> | Utility | v1.4 | 4.9.7       |                |              |       |               |               |            | -  |    |            |    |

|--------|---------|--------|--------------|---------|------|-------------|----------------|--------------|-------|---------------|---------------|------------|----|----|------------|----|

| Access | ; Sp    | ecific | Wir          | ndow    | Н    | elp         |                |              |       |               |               |            |    |    |            |    |

|        | 1       | idex   | -            | (inde   | ní – | 10<br>space | 10.<br>(index) | SI           | 0     | $\mathcal{V}$ | SPD           | ]n<br>(sm) |    |    | 7ª<br>ACPI |    |

| E PC   | л<br>П  |        |              |         |      | _           |                |              |       |               |               |            |    | _  |            |    |

|        | F       | ) C    | bin          | È.      | å    |             |                | byte<br>8bit | wo    |               | word<br>2 bit | ì          |    |    |            |    |

|        | <u></u> |        |              |         |      |             |                |              |       |               |               |            |    |    |            |    |

| Bus (  | )0, D   | evice  | e 1 F, F     | Funct   | ion  | 00 - Int    | tel Co         | rpor         | ation | ISA B         | Bridge        | 9          |    |    |            | •  |

| 220    | 00      | 01     | 02           | 03      | 04   | 05          | 06             | 07           | 08    | 09            | 0A            | 0B         | 0C | 0D | 0E         | 0F |

| 00     | 86      | 80     | 17           | 29      | 07   | 01          | 10             | 02           | 03    | 00            | 01            | 06         | 00 | 00 | 80         | 00 |

| 10     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| 20     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 28 | 10 | 33         | 02 |

| 30     | 00      | 00     | 00           | 00      | E0   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| 40     | 01      | 10     | 00           | 00      | 80   | 00          | 00             | 00           | 81    | 10            | 00            | 00         | 10 | 00 | 00         | 00 |

| 50     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| 60     | 83      | 8A     | 8B           | 8A      | D1   | 00          | 00             | 00           | 8A    | 83            | 8B            | 80         | F8 | 00 | 00         | 00 |

| 70     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| 80     | 00      | 00     | 04           | 3C      | 01   | 09          | 7C             | 00           | 00    | 00            | 00            | 00         | 81 | 0C | 3C         | 00 |

| 90     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| A0     | 20      | 0E     | 00           | 00      | 39   | 02          | 80             | 00           | 2B    | 1C            | 4A            | 00         | 00 | 03 | 00         | 40 |

| BO     | 00      | 00     | F0           | 00      | 00   | 00          | 00             | 00           | 08    | 00            | 01            | 00         | 00 | 00 | 00         | 00 |

| C0     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 00    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| DO     | 00      | 00     | 00           | 00      | 00   | 00          | 00             | 00           | 80    | F0            | 00            | 00         | 08 | 00 | 00         | 00 |

| E0     | 09      | 00     | 0C           | 10      | 00   | 02          | C4             | 03           | 04    | 00            | 00            | 00         | 00 | 00 | 00         | 00 |

| F0     | 01      | 80     | D1           | FE      | 00   | 00          | 00             | 00           | 86    | 0F            | 03            | 00         | 00 | 00 | 00         | 00 |

| Hardw  | are     |        |              |         |      |             |                |              |       |               |               |            |    |    |            |    |

- Look at the BIOS\_CNTL register in the LPC device

- BIOS Lock Enable (BLE) bit 1 is not asserted

- This means any application privileged enough to either map the PCI Express configuration space or perform port I/O can assert BIOSWE to enable writes to the BIOS flash

### vulnBIOS example: BIOS\_CNTL Testing

|           |        |        | _       |       | y v1.4 |             |               |             |          |               |        |      |    |    |            |    |

|-----------|--------|--------|---------|-------|--------|-------------|---------------|-------------|----------|---------------|--------|------|----|----|------------|----|

| Access    | s Sp   | ecific | : Wi    | indow | / He   | lp          |               |             |          |               |        |      |    |    |            |    |

| <b>12</b> |        | idex   | <u></u> | ind   |        | I Ø.<br>BCE | 10<br>(index) | ISI<br>0101 |          | $\mathcal{V}$ | SPD    | In   |    |    | 72<br>ACPI |    |

| PC        | I      |        |         |       |        |             |               |             |          |               | _      |      |    |    | _          |    |

|           | F      | N D    | bin     | è     | Â      | N           |               | byte        | wo       |               | word   | 4    |    |    |            |    |

|           | ų,     | i l    |         |       |        |             |               | 8bit        | 16       | bit 3         | 2bit   | 4    |    |    |            |    |

| Bus 0     | )0, De | evice  | 1F, I   | Funct | ion 0  | 0 - Int     | el Co         | rpora       | ation    | ISAE          | Bridge | Э    |    |    |            | •  |

| 220       | 00     | 01     | 02      | 03    | 04     | 05          | 06            | 07          | 08       | 09            | 0A     | 0B   | 0C | 0D | 0E         | 0F |

| 00        | 86     | 80     | 17      | 29    | 07     | 01          | 10            | 02          | 03       | 00            | 01     | 06   | 00 | 00 | 80         | 00 |

| 10        | 00     | 00     | 00      | 00    | 00     | 00          | 00            | 00          | 00       | 00            | 00     | 00   | 00 | 00 | 00         | 00 |

| 20        | 00     | 00     | 00      | PCT   | 00,1F, | 00 Re       | a OD          | c (220      | ))       |               |        | 2    | x  | 10 | 33         | 02 |

| 30        | 00     | 00     | 00      |       | 00,11, | 00110       | .g 00.        | - (22)      | <i>"</i> |               |        | _    |    | 00 | 00         | 00 |

| 40        | 01     | 10     | 00      |       | 7 6    | 5           | 4 3           | 2           | 1        | 0 r           |        |      | _  | 00 | 00         | 00 |

| 50        | 00     | 00     | 00      |       |        | 0           | 0 1           | 0           | 1        |               | De     | one  |    | 00 | 00         | 00 |

| 60        | 83     | 8A     | 8B      | r -   |        |             | OB            |             |          | n r           |        |      |    | 00 | 00         | 00 |

| 70        | 00     | 00     | 00      |       |        |             | UD            |             |          | !             | La     | ncel |    | 00 | 00         | 00 |

| 80        | 00     | 00     | 04      |       |        |             |               |             |          |               |        |      |    | 0C | 3C         | 00 |

| 90        | 00     | 00     | 00      | 00    | 00     | 00          | 00            | 00          | D.S      | 00            | 00     | 00   | 00 | 00 | 00         | 00 |

| A0        | 20     | 0E     | 00      | 00    | 39     | 02          | 80            | 00          | 2B       | ю             | 4A     | 00   | 00 | 03 | 00         | 40 |

| BO        | 00     | 00     | F0      | 00    | 00     | 00          | 00            | 00          | 08       | 00            | 01     | 00   | 00 | 00 | 00         | 00 |

| C0        | 00     | 00     | 00      | 00    | 00     | 00          | 00            | 00          | 00       | 00            | 00     | 00   | 00 | 00 | 00         | 00 |

| D0        | 00     | 00     | 00      | 00    | 00     | 00          | 00            | 00          | 80       | F0            | 00     | 00   | OB | 00 | 00         | 00 |

| E0        | 09     | 00     | 0C      | 10    | 00     | 02          | C4            | 03          | 04       | 00            | 00     | 00   | 00 | 00 | 00         | 00 |

| F0        | 01     | 80     | D1      | FE    | 00     | 00          | 00            | 00          | 86       | 0F            | 03     | 00   | 00 | 00 | 00         | 00 |

| Hardw     | are    |        |         |       |        |             |               |             |          |               |        |      |    |    |            |    |

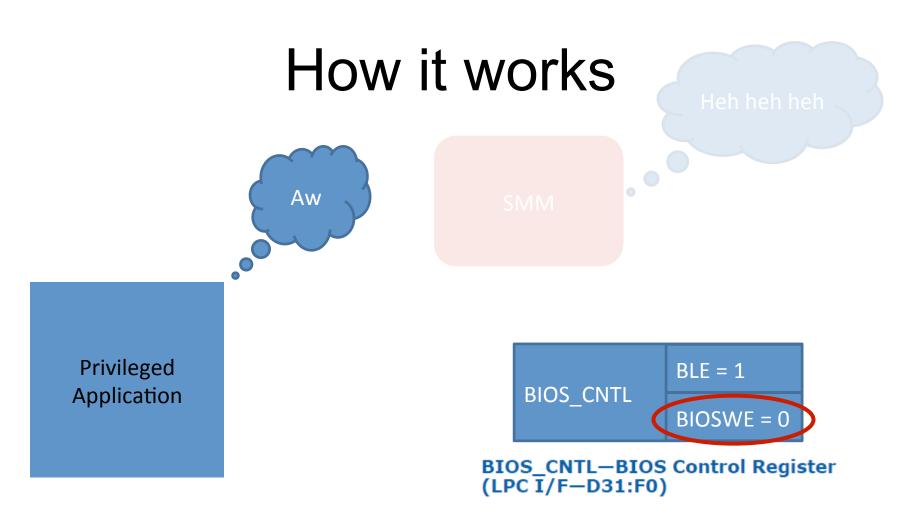

- You don't have to do this, but note that it is possible to set BIOS Lock Enable to 1 and not have an SMI handler routine running that checks and de-asserts BIOS Write Enable bit 0

- We've seen this on multiple systems; where BLE was set, but asserting BIOSWE to 1 was not reset to 0

- This is why bit 0 must be tested in order to really test write-protection

### vulnBIOS example: BIOS\_CNTL Testing: Set BLE

|           | ead & Write | _        |          |            |                |              |          |               |          |          |          | -        |       |                        |          |     |

|-----------|-------------|----------|----------|------------|----------------|--------------|----------|---------------|----------|----------|----------|----------|-------|------------------------|----------|-----|

| Access S  | pecific W   | indow    | He       | lp         |                |              |          |               |          |          |          |          |       |                        |          |     |

|           | index 📟     | l 🛄      |          | 16<br>18ce | <u>Index</u>   |              |          |               | SI       |          | (smbus   | MS       |       | 7 <sup>2</sup><br>ACPI | 5        | C C |

| 📕 IO Spac | ce          |          |          |            |                |              |          |               |          |          |          |          |       |                        |          |     |

|           |             | ÅÅ       |          |            | oyte  <br>Bbit | word<br>16bi | d dw     | vord<br>2 bit | ì        |          |          |          |       |                        |          |     |

|           |             | Sale and | _        | <u> </u>   |                |              |          |               | _        |          |          |          |       |                        |          | _   |

| IO Sp     | ace Bas     | e = 0    | 0B2      |            |                |              |          |               |          |          |          |          |       |                        |          | Γ   |

| 0         | 0100        | 0302     |          | 0504       | ŧ              | 0706         | 5        | 0908          | 8        | 0B0/     | A        | 0D0      | с     | 0F0                    | E        | ſ   |

| 00        | B105        | FF00     |          | FFFF       | -              | FF00         | )        | FFF           | F        | FF0      | 0        | FFF      | F     | 5F4                    | 0        |     |

| 10        | FFEF        | Bus (    |          |            |                | Eurot        | ion O    | 0 1+          |          |          | otion    |          | Drida | _                      |          |     |

| 20        | FFFF        | Dusi     | JU, DI   | evice      | 9.1E, 1        | Tunci        | ion o    | 0 - Ini       | ercu     | прои     | auon     | ISAL     | onug  | e                      |          |     |

| 30        | FFFF        | 220      | 00       | 01         | 02             | 03           | 04       | 05            | 06       | 07       | 08       | 09       | 0A    | 0B                     | 0C       | 0   |

|           |             | 00       | 86       | 80         | 17             | 29           | 07       | 01            | 10       | 02       | 03       | 00       | 01    | 06                     | 00       | 00  |

|           | · \         | 10<br>20 | 00<br>00 | 00<br>00   | 00<br>00       | 00<br>00     | 00<br>00 | 00<br>00      | 00<br>00 | 00<br>00 | 00<br>00 | 00<br>00 | 00    | 00<br>00               | 00<br>28 | 00  |

|           |             | 30       | 00       | 00         | 00             | 00           | EO       | 00            | 00       | 00       | 00       | 00       | 00    | 00                     | 00       | 0   |

|           |             | 40       | 01       | 10         | 00             | 00           | 80       | 00            | 00       | 00       | 81       | 10       | 00    | 00                     | 10       | 0   |

|           |             | 50       | 00       | 00         | 00             | 00           | 00       | 00            | 00       | 00       | 00       | 00       | 00    | 00                     | 00       | 0   |

|           |             | 60       | 82       | 8A         | 8B             | 8A           | D1       | 00            | 00       | 00       | 8A       | 83       | 8B    | 80                     | F8       | 0(  |

|           |             | 70       | 00       | 90         | 00             | 00           | 00       | 00            | 00       | 00       | 00       | 00       | 00    | 00                     | 00       | 00  |

|           |             | 80<br>90 | 00<br>00 | 00         | 04<br>00       | 3C<br>00     | 01<br>00 | 09<br>00      | 7C<br>00 | 00<br>00 | 00<br>00 | 00<br>00 | 00    | 00                     | 81<br>00 | 00  |

|           |             | 90<br>A0 | 20       | 00<br>0E   | 00             | 00           | 29       | 00            | 80       | 00       | 2B       | 1C       | 4A    | 00                     | 00       | 03  |

|           |             | BO       | 00       | 00         | F0             | 00           | 00       | 00            | 00       | 00       | 08       | 00       | 01    | 00                     | 00       | 0   |

|           |             | C0       | 00       | 00         | 00             | 00           | 00       | 00            | 00       | 80       | 00       | 00       | 00    | 00                     | 00       | 0(  |

|           |             | DO       | 00       | 00         | 00             | 00           | 00       | 00            | 00       | 00       | 80       | F0       | 00    | ×                      | 0A       |     |

|           |             | E0       | 09       | 00         | 0C             | 10           | 00       | 02            | C4       | 03       | 04       | 00       | 00    | 00                     | -00      | 0   |

- Now we're going to setup BIOS\_CNTL so that it protects the flash

- <u>This will only work on</u> <u>these lab machines with</u> <u>this modified BIOS</u>

- I inserted a custom SMI handler that resets the BIOSWE bit to 0 if it is asserted

- We're going to enable this by writing the word 0xb105 to port 0xB2

- You should now see the BLE bit asserted in BIOS\_CNTL (0x0A)

## vulnBIOS example: BIOS\_CNTL Testing

| 📕 PC  | I      |        |       |       |        |          |       |                           |       |       |            |    |    |    |    |    |

|-------|--------|--------|-------|-------|--------|----------|-------|---------------------------|-------|-------|------------|----|----|----|----|----|

|       | F      | ) e    | bin   | R     | å      | 8        |       | byte<br><mark>8bit</mark> | wo    |       | word       | à  |    |    |    |    |

|       |        |        |       |       |        | <u> </u> |       |                           |       |       | ZUIQ       |    |    |    |    |    |

| Bus ( | )0, Di | evice  | 1F, I | Funct | tion 0 | 0 - Int  | el Co | rpor                      | ation | ISA E | Bridg      | e  |    |    |    | •  |

| 220   | 00     | 01     | 02    | 03    | 04     | 05       | 06    | 07                        | 08    | 09    | <b>0</b> A | 0B | 0C | 0D | 0E | 0F |

| 00    | 86     | 80     | 17    | 29    | 07     | 01       | 10    | 02                        | 03    | 00    | 01         | 06 | 00 | 00 | 80 | 00 |

| 10    | 0      | PCI 00 | 1F.00 | ) Rea | 0DC    | (220)    |       |                           |       | x     |            | 00 | 00 | 00 | 00 | 00 |

| 20    | 0      |        |       |       |        | (,       |       |                           |       |       |            | 00 | 28 | 10 | 33 | 02 |

| 30    | 0      | 7      | 6     | 5 4   | 3      | 2 1      | 0     |                           |       |       |            | 00 | 00 | 00 | 00 | 00 |

| 40    | 0      | 0      | 0     | 0 0   | 1      | 0 1      | 1     |                           | Don   | e     |            | 00 | 10 | 00 | 00 | 00 |

| 50    | 0      |        | -     |       | OB     | _        |       |                           | Cano  | -     |            | 00 | 00 | 00 | 00 | 00 |

| 60    | 8      | I      |       |       | 00     |          |       |                           | Lanc  | e     |            | 80 | F8 | 00 | 00 | 00 |

| 70    | 0      |        |       |       |        | -        | _     |                           |       |       |            | 00 | 00 | 00 | 00 | 00 |

| 80    | 00     | 00     | 04    | 3C    | 01     | 09       | х     | 00                        | 00    | 00    | 00         | 00 | 81 | 0C | 3C | 00 |

| 90    | 00     | 00     | 00    | 00    | 00     | 00       | 00    | 60                        | 00    | 00    | 00         | 00 | 00 | 00 | 00 | 00 |

| A0    | 20     | 0E     | 00    | 00    | 39     | 00       | 80    | 00                        | 28    | 1C    | 4A         | 00 | 00 | 03 | 00 | 40 |

| BO    | 00     | 00     | F0    | 00    | 00     | 00       | 00    | 00                        | 08    | 00    | 01         | 00 | 00 | 00 | 00 | 00 |

| C0    | 00     | 00     | 00    | 00    | 00     | 00       | 00    | 00                        | 00    | 00    | 00         |    | 00 | 00 | 00 | 00 |

| D0    | 00     | 00     | 00    | 00    | Bit    | 0 is     | s de  | e-as                      | sse   | rte   | d          | 00 | 0A | 00 | 00 | 00 |

| E0    | 09     | 00     | 00    | 1     | 0.0    |          |       |                           |       | 0.5   |            | 00 | 00 | 00 | 00 | 00 |

| F0    | 01     | 80     | D1    | FE    | 00     | 00       | 00    | 00                        | 86    | 0F    | 03         | 00 | 00 | 00 | 00 | 00 |

| Hardw | are    |        |       |       |        |          |       |                           |       |       |            |    |    |    |    |    |

- Now try to enable writes to the BIOS by asserting BIOSWE bit 0

- Set BIOS\_CNTL to 0x0B

- You will notice that it resets to 0x0A

- This is the SMI handler working as it should

- Note the reset of BIOSWE to 0 occurs during SMM

- Any tangible delay you see in resetting this value is due to the (configurable) "Refresh"

button in RW-E

# BIOSWE/BLE should be considered deprecated!

- We can defeat it on systems that are not using SMRRs

- "The Sicilian" "<u>Defeating Signed BIOS enforcement</u>", Kallenberg et al., EkoParty 2013

- We can defeat it on systems that don't set SMI\_LOCK

- "Charizard" "<u>Setup for Failure: Defeating UEFI Secure Boot</u>", Kallenberg et al., Syscan 2014

- But Charizard actually found by Sam Cornwell, it just got merged into Corey's talk in its first appearance. Will be spun off later.

- We can defeat it on systems TXT-enabled that suppress SMIs

- "Sandman" "SENTER Sandman: Using Intel TXT to attack BIOSes", Kovah et al., Summercon 2014

- We have a new fundamental attack against it that will bypass BLE on all systems, once and for all. "Speed Racer" We'll talk about these at the end, depending on time.

# BIOS\_CNTL: SMM\_BWP

#### BIOS\_CNTL—BIOS Control Register (LPC I/F—D31:F0)

|   | Offset A<br>Default<br>Lockabl |                                      | DCh<br>20h<br>No                                |                                                                                                                                                                                    | Attribute:<br>Size:<br>Power Well:                                                                                                   | R/WLO, R/W, RO<br>8 bits<br>Core                                                                          |

|---|--------------------------------|--------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| [ | Bit                            |                                      |                                                 | De                                                                                                                                                                                 | scription                                                                                                                            |                                                                                                           |

| ľ | 7:6                            | Reserved                             |                                                 |                                                                                                                                                                                    |                                                                                                                                      |                                                                                                           |

|   |                                | SMM BI                               | OS Wri                                          | te Protect Disable (SM                                                                                                                                                             | M_BWP)-R/WL.                                                                                                                         |                                                                                                           |

| ( | 5                              | 0 = BIOS<br>proce<br>1 = BIOS        | 6 region<br>essors a<br>6 region                | are in SMM or not. (Set t                                                                                                                                                          | bled. The BIOS Reg<br>this field to 0 for leg<br>led. The BIOS Regi                                                                  | ion is writable regardless if<br>gacy behavior).<br>on is not writable unless all                         |

|   | 4                              |                                      |                                                 | <del>us (TSS)</del> —RO. This bit<br>t that is at offset 3414h,                                                                                                                    |                                                                                                                                      | ly path to view the state of                                                                              |

|   | 3:2                            | BIOS rea<br>Bit 3 – Pi<br>Bit 2 – Ca | ds on t<br>refetch<br>ache Di<br>are sun<br>3:2 | he SPI interface:<br>Enable<br>sable<br><b>Description</b><br><b>No prefetching, but c</b><br>the read buffer cache w<br>fetches to the same line<br><b>No prefetching and n</b> e | aching enabled. 6<br>ith "valid" data, allo<br>to complete quickl<br>o caching. One-to-<br>cycles. This value c<br>ing enabled. This | owing repeated code<br>ly.<br>one correspondence of<br>can be used to invalidate<br>mode is used for long |

|   | 1                              | 0 = Trans<br>1 = Enab                | sition of<br>les sett                           | ble (BLE)—R/WLO.<br>f BIOSWE from `0' to `1'<br>ting the BIOSWE bit to c<br>be cleared by a PLTRST                                                                                 | ause SMIs and lock                                                                                                                   | MI to be asserted.<br>s SMM_BWP. Once set, this                                                           |

|   | 0                              | 0 = Only<br>1 = Acce<br>writt        | read cy<br>ss to th<br>en from                  | able (BIOSWE)—R/W.<br>ycles result in Firmware<br>e BIOS space is enabled<br>n a 0 to a 1 and BIOS Lo<br>This ensures that only Si                                                 | for both read and v<br>ck Enable (BLE) is                                                                                            | write cycles. When this bit is<br>also set, an SMI# is                                                    |

- In PCH chipsets, bit 5 of BIOS\_CNTL has been defined:

- Provides the vendor the ability to ensure that BIOS region may ONLY be written to when all processors are in SMM and BIOSWE is enabled

- Our lab system does not implement this bit because it is an MCH/ICH system, but check it out on your own

- As we've seen, this register is important to lock down the BIOS to mitigate SMI suppression

- Same here

- Only 6 out of ~10k systems we've measured to date use it!!! <sup>(3)</sup>

- As of 3/31/2014

# **Another Protection Mechanism**

#### Table 5-60. Flash Protection Mechanism Summary

|           | Mechanism                         | Accesses<br>Blocked | Range<br>Specific? | Reset-Override<br>or SMI#-<br>Override? | Equivalent Function on<br>FWH                     |

|-----------|-----------------------------------|---------------------|--------------------|-----------------------------------------|---------------------------------------------------|

| $\langle$ | BIOS Range<br>Write<br>Protection | Writes              | Yes                | Reset Override                          | FWH Sector Protection                             |

|           | Write Protect                     | Writes              | No                 | SMI# Override                           | Same as Write Protect in<br>previous ICHs for FWH |

- BIOS Range Write-Protection is the second major line of defense

- There are 5 Protected Range registers (0-4) with independent R/W permissions

- Setting these will prevent reads and/or writes until the system is reset.

\* Information on FWH Sector Protection is hard to come by. It appears to be a security mechanic on the chip itself, since chips can be described as being divided into sectors.

#### PR0—Protected Range 0 Register (SPI Memory Mapped Configuration Registers)

Memory Address: Default Value: 00000000h

Attribute: Size: R/W 32 bits So who protects the protector?

This guy that's who!

We'll get to that later

This register can not be written when the FLOCKDN bit is set to 1.

| Bit   | Description                                                                                                                                                                                                                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Write Protection Enable — R/W. When set, this bit indicates that the Base and Limit fields in this register are valid and that writes and erases directed to addresses between them (inclusive) must be blocked by hardware. The base and limit fields are ignored when this bit is cleared.                     |

| 30:29 | Reserved                                                                                                                                                                                                                                                                                                         |

| 28:16 | <b>Protected Range Limit</b> — R/W. This field corresponds to FLA address bits 24:12 and specifies the upper limit of the protected range. Address bits 11:0 are assumed to be FFFh for the limit comparison. Any address greater than the value programmed in this field is unaffected by this protected range. |

| 15    | <b>Read Protection Enable</b> — R/W. When set, this bit indicates that the Base and Limit fields in this register are valid and that read directed to addresses between them (inclusive) must be blocked by hardware. The base and limit fields are ignored when this bit is cleared.                            |

| 14:13 | Reserved                                                                                                                                                                                                                                                                                                         |

| 12:0  | <b>Protected Range Base</b> — R/W. This field corresponds to FLA address bits 24:12 and specifies the lower base of the protected range. Address bits 11:0 are assumed to be 000h for the base comparison. Any address less than the value programmed in this field is unaffected by this protected range.       |

# Protected Range (PR) Registers

- The protections prescribed herein are enforced even upon the SMI handler

- Enforced on register access, not direct access, however

- Protected ranges are available to a SPI flash operating in either Non-Descriptor mode or Descriptor mode

- The ranges don't have to mirror descriptor mode regions

- Base addresses must be page-aligned

- Lower 12 bits are 000h

- Limit addresses end at one under a page aligned boundary

- Lower 12 bits are FFFh

- Addresses are Flash Linear Addresses (FLAs)

- Basically an offset from the base of the flash

- So "offset" 0x260000 on the flash is Flash Linear Address 0x260000

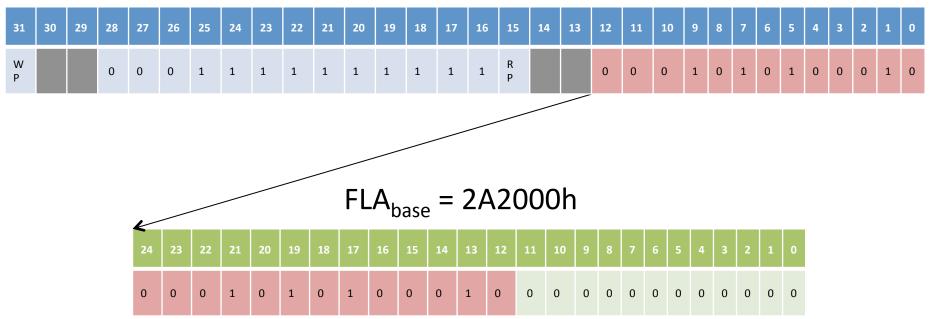

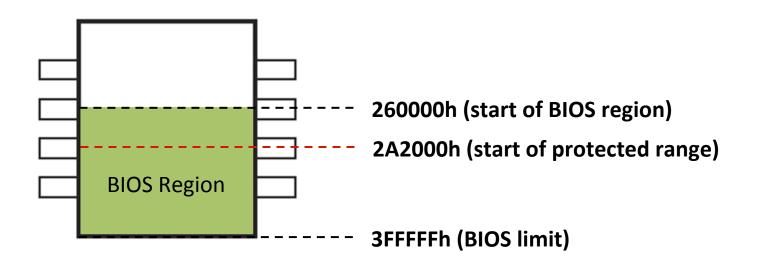

### PR Sample: 03FF02A2h Base 2A2000h

**Protected Range Base**

- To set a PR from a Flash Linear Address Limit:

- PR<sub>base</sub> = ((page-aligned FLA<sub>base</sub>) & FFF000) >> 12

- $PR_{base} = 2A2 = 000002A2h$

- To write-protect this range: PR0 | = 80000000h

- To read-protect this range: PR0 |= 00008000h

\*We're picking a funny base because the offset at the real BIOS base is normally all 0xFF's so it's harder to illustrate the point. This example will show us a visible boundary whereas the real BIOS base address would not.

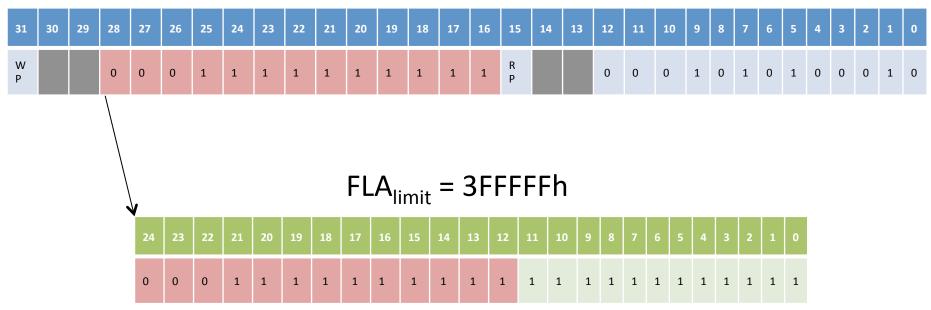

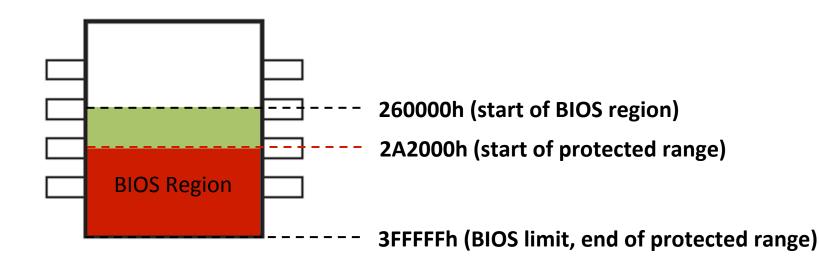

### PR Example: 03FF02A2h Limit 3FFFFh

#### **Protected Range Limit**

- To set a PR from a Flash Linear Address Limit:

- PR<sub>limit</sub> = (page-aligned FLA<sub>limit</sub>) << 16

- PR<sub>limit</sub> = 3FF000 << 4 = 03FF02A2h

- To write-protect this: PR | = 8000000h

- To read-protect this: PR |= 00008000h

### vulnBIOS Example: Protected Range Registers

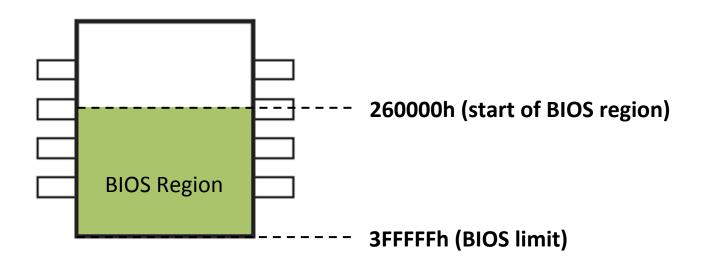

- On our lab E6400, the BIOS region occupies the range 260000 – 3FFFFh on the physical chip

- 260000h and 3FFFFFh are Flash Linear Addresses (FLAs)

- The CPU/BIOS (including us using RW-E) always has Read/ Write access the BIOS region on flash

- Per the flash master permission settings

### vulnBIOS Example: Protected Range Registers

- The previous slides set up a protected range from 2A2000h to 3FFFFh

- PR = 03FF02A2h (has not yet been read/write protected)

- On our lab machines, this covers a portion of our BIOS region

### vulnBIOS Example: Protected Range Registers

- Let's first verify we can read this by viewing the BIOS dump from Copernicus

- PR = 03FF02A2h (has not yet been read/write protected)

- On our lab machines, this covers a portion of our BIOS region

### vulnBIOS example: Protected Range Registers

| Copernicus_BIOS. | bin |    |    |               |    |    |    |    |               |    |    |    |    |                        |    |       |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

|------------------|-----|----|----|---------------|----|----|----|----|---------------|----|----|----|----|------------------------|----|-------|----|---|---|----|-----|-----|-----|--------------|----|------------|-----|-----|-----|----|----|----|------|

| Offset(h)        | 00  | 01 | 02 | 03            | 04 | 05 | 06 | 07 | 08            | 09 | 0A | 0в | 0C | 0D                     | 0E | 0F    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FA0         | 00  | 1E | D3 | 52            | F1 | AF | A1 | 9в | D1            | AA | 21 | 35 | 71 | 83                     | 61 | E6    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FB0         | 92  | 64 | 80 | 48            | 47 | 5F | 49 | 53 | 5F            | 49 | 4D | 4D | 12 | E1                     | F5 | F3    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FC0         | 00  | FO | 46 | EB            | F1 | A6 | E1 | D8 | 43            | EB | F1 | EB | F5 | F3                     | ЕO | 0в    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FD0         | F3  | 3в | 00 | 57            | E4 | 1F | 60 | 0C | 40            | 54 | 4F | 4B | 45 | 4E                     | 72 | 46    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FE0         | 21  | 28 | 71 | D5            | F3 | 53 | 00 | 99 | Α4            | 2F | 00 | 0в | D3 | E7                     | D5 | DE    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A1FF0         | 92  | 43 | 44 | 37            | 00 | 22 | 84 | FF | C2            | Α9 | F1 | 1B | F2 | DE                     | E2 | CD    |    | _ |   | 2  | • • |     |     |              | וח | <b>ה</b> ( | ст. |     |     |    |    |    |      |

| 002A2000         | F1  | C3 | D2 | 1B            | F4 | A3 | 10 | 0E | D1            | C4 | FF | E1 | 99 | D1                     | 8B | D1    |    |   | 4 | Zŀ | 42  | 200 | JUI | n (          | P  | K S        | Sta | arı | []  |    |    |    |      |

| 002A2010         | 33  | A1 | D2 | 00            | 44 | 02 | 34 | 10 | 54            | 62 | C2 | 20 | F3 | $\mathbf{F}\mathbf{F}$ | 00 | 1C    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A2020         | 26  | 73 | 83 | 77            | 91 | 50 | 71 | в0 | 8B            | 7в | F3 | C3 | 10 | 4B                     | 54 | F4    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 002A2030         | 0F  | E3 | 4E | 91            | 5B | 92 | CA | 53 | $\mathbf{FB}$ | 74 | в3 | 00 | 53 | 05                     | 17 | E2    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| •                |     |    |    |               |    |    | •  |    |               |    |    |    |    |                        | •  |       |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| •                |     |    |    |               |    |    | •  |    |               |    |    |    |    |                        | •  |       |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| •                |     |    |    |               |    |    | •  |    |               |    |    |    |    |                        | •  |       |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFF90         | 90  | ΕA | F0 | $\mathbf{FF}$ | 30 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFA0         | 00  | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFB0         | 00  | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFC0         | 00  | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFD0         | 00  | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFE0         | 00  | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    |   |   |    |     |     |     |              |    |            |     |     |     |    |    |    |      |

| 003FFFF0 1       | E9  | 3D | FE | 00            | 00 | 00 | 00 | 00 | 00            | 00 | 00 | 00 | 00 | 00                     | 00 | 00    |    | _ |   | 21 | CC  | CC  | Ch  | ۱ <b>(</b> ا | DE | ) F        | 'n  | 4 ( | RI  | nc | 11 | mi | it)) |

| offset: 2A2000   |     |    |    |               |    |    |    |    |               |    |    |    |    |                        |    | Overw | /r |   | • | J  |     |     |     | . (          |    | <b>\ L</b> |     | ч ( | יוט | 53 | LI |    | 5    |

- First let's establish that we have permission to read the BIOS region

- Run Copernicus and open the .bin file with your favorite hex editor (HxD is a good one for Windows)

- Observe binary range 2A2000-3FFFFh

- Looks like BIOS to me!

### vulnBIOS example: Protected Range Registers

| 🔣 Memory           |          |                          |          |          |  |  |  |  |  |  |  |  |  |  |

|--------------------|----------|--------------------------|----------|----------|--|--|--|--|--|--|--|--|--|--|

|                    |          | byte word<br><b>8bit</b> |          | ?        |  |  |  |  |  |  |  |  |  |  |

| Address = FED1B800 |          |                          |          |          |  |  |  |  |  |  |  |  |  |  |

| 116                | 03020100 | 07060504                 | 0B0A0908 | 0F0E0D0C |  |  |  |  |  |  |  |  |  |  |

| 00                 | 03FF0260 | 3F006009                 | 003FFFC0 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 10                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 20                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 30                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 40                 | 00FE3DE9 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 50                 | 00001F1F | 00000000                 | 03FF0260 | 025F000B |  |  |  |  |  |  |  |  |  |  |

| 60                 | 00020001 | 000A0003                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 70                 | 00000000 | 03FF82A2                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 80                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| 90                 | 00406004 | 4FC80606                 | 029FABAB | 01050220 |  |  |  |  |  |  |  |  |  |  |

| A0                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| BO                 | 00003008 | 1F1F0218                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| C0                 | 0000007  | 00002005                 | 00002005 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| D0                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| E0                 | 00000000 | 00000000                 | 00000000 | 00000000 |  |  |  |  |  |  |  |  |  |  |

| F0                 | 0000000  | 00000000                 | 00000000 | 0000000  |  |  |  |  |  |  |  |  |  |  |

| Hardware           |          |                          |          |          |  |  |  |  |  |  |  |  |  |  |

- To Write-protect a range:

- PR | = 8000000h

- To Read-protect a range:

- PR |= 00008000h

- For this example let's disable reads to this range:

- Set PR0 (at 74h) to 03FF82A2h

### vulnBIOS example: Protected Range Registers

|     | Copernicus_BIOS | S.bin |    |    |      |    |    |    |    |      |     |     |    |     |    |               |       |    |               |          |       |          |      |      |

|-----|-----------------|-------|----|----|------|----|----|----|----|------|-----|-----|----|-----|----|---------------|-------|----|---------------|----------|-------|----------|------|------|

|     | Offset(h)       | 00    | 01 | 02 | 03   | 04 | 05 | 06 | 07 | 08   | 09  | 0A  | 0в | 0C  | 0D | 0E            | 0F    |    |               |          |       |          |      |      |

|     | 002A1FA0        | 00    | 1E | D3 | 52   | F1 | AF | A1 | 9в | D1   | AA  | 21  | 35 | 71  | 83 | 61            | E6    |    |               |          |       |          |      |      |

|     | 002A1FB0        | 92    | 64 | 80 | 48   | 47 | 5F | 49 | 53 | 5F   | 49  | 4D  | 4D | 12  | E1 | F5            | F3    |    |               |          |       |          |      |      |

|     | 002A1FC0        | 00    | FO | 46 | EB   | F1 | A6 | E1 | D8 | 43   | EB  | F1  | EB | F5  | F3 | E0            | 0в    |    |               |          |       |          |      |      |

|     | 002A1FD0        | F3    | 3в | 00 | 57   | E4 | 1F | 60 | 0C | 40   | 54  | 4F  | 4B | 45  | 4E | 72            | 46    |    |               |          |       |          |      |      |

|     | 002A1FE0        | 21    | 28 | 71 | D5   | F3 | 53 | 00 | 99 | A4   | 2F  | 00  | 0в | D3  | E7 | D5            | DE    |    |               |          |       |          |      |      |

|     | 002A1FF0        | 92    | 43 | 44 | 37   | 00 | 22 | 84 | FF | C2   | Α9  | F1  | 1B | F2  | DE | E2            | CD    | 24 | 2000          |          | C 4 4 | <b>`</b> |      |      |

|     | 002A2000        | FF    | FF | PT | F.F. | FF | FF | FF | FF | E.F. | E F | FF  | FF | FF  | FF | FF            | FF    | ZP | <b>2000</b> ł | ו (אר) ו | Start | )        |      |      |

|     | 002A2010        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FΕ  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 00272020        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 002A2030        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     |                 |       |    |    |      |    |    | •  |    |      |     |     |    |     |    | •             |       |    |               |          |       |          |      |      |

|     |                 |       |    |    |      |    |    |    |    |      |     |     |    |     |    |               |       |    |               |          |       |          |      |      |

| - 1 |                 |       |    |    |      |    |    |    |    |      |     |     |    |     |    |               |       | 1  |               |          |       |          |      |      |

|     |                 |       |    |    |      |    |    | •  |    |      |     |     |    |     |    | •             |       |    |               |          |       |          |      |      |

| _ \ | 003FFF90        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 003FFFA0        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 003FFFB0        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 003FFFC0        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 003FFFD0        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | FF  | FF | F'F           | FF    |    |               |          |       |          |      |      |

|     | 003FFFE0        | FF    | FF | FF | FF   | FF | FF | FF | FF | FF   | FF  | FF  | FF | E T | FF | FF            | FF    |    |               |          |       |          |      |      |

|     | 003FFFF0        | FF    | ΕE | FF | FF   | FF | FF | FF | FF | FF   | F F | E E | FF | FF  | FF | $\mathbf{FF}$ | FF    | 20 | FFFFh         |          | nd (I |          | limi | i+\\ |

|     | Offset: 3FFFFF  |       |    |    |      |    |    |    |    |      |     |     |    |     |    |               | Overw | 5  | TTTTI         |          |       | 500      |      | ·//  |

|     | L               |       | -  |    | -    |    |    |    |    | -    |     |     | -  |     | -  | -             |       |    |               |          |       |          |      |      |

- Now re-run Copernicus and view the BIOS binary file in a hex editor

- As you can see the Protected Range registers override the Flash Master permissions

- This is the BIOS region to which the CPU/BIOS Master otherwise "always" has permission to read and write

# PR Summary:

- Implementing Protected Ranges is an important strategy for locking down a system BIOS

- Without PR's, any bypass of SMM's global write-protection means an attacker is automatically able to modify the BIOS

- Protected Range register enforcement:

- Overrides the Flash Master permissions

- Prevents Reads/Writes directly from the flash, even when the processor is running in SMM

- We did not demonstrate this, but it is true

- Because of this, BIOS updates (or updates to protected ranges) must be performed before the Protected Ranges are configured by the BIOS

- Only the vendor can reliably configure PR's since new UEFI BIOSes had a region of naturally changing content

# **FLOCKDN Register**

- When we were been able to easily modify (and remodify) registers in the SPI configuration registers that are designed to protect the system

- For example, we can configure and modify the protected range registers to suit the needs of a lab

- But if we can change them, so can any other app capable of mapping X

- Intel provides the FLOCKDN register to solve this problem

# FLOCKDN

#### HSFS—Hardware Sequencing Flash Status Register (SPI Memory Mapped Configuration Registers)

Memory Address: Default Value: 0000

0000h + 04h

Attribute: Size: RO, R/WC, R/W 16 bits

Bit

Description

15

Flash Configuration Lock-Down (FLOCKDN) — R/W/L. When set to 1, those Flash Program Registers that are locked down by this FLOCKDN bit cannot be written. Once set to 1, this bit can only be cleared by a hardware reset due to a global reset or host partition reset in an Intel ME enabled system.

- FLOCKDN, when asserted, prevents certain configuration registers/bits in the SPI BAR from being changed

- Once asserted, FLOCKDN cannot be reset to 0 until a reset

Or can it? :) Snorlax & Darth Venamis on Day 5!

- Although hardware-sequencing is available only in descriptor mode, the FLOCKDN bit still provides register lock-down protection when the flash is operating in non-descriptor mode

- Called SPI or Flash Configuration Lock-Down bit

# **FLOCKDN** Affected Registers

(see *your* manual, but at the time of original class generation...)

- 1. Flash Regions Access Permissions Register (

- bits 31:24 (BMWAG) and bits 23:16 (BMRAG)

- 2. Protected Range (PR) registers 0 to 4

- entire register is locked

- 3. Software Sequencing Flash Control Register (SSFC)

- bits 18:16

- Configure SPI Cycle Frequency (20 MHz, 33 MHz, or 50 MHz [PCH only])

- 4. Prefix Opcode Configuration Register (PREOP)

- entire register is locked

- 5. Opcode Type Configuration Registers (OPTYPE)

- Entire register is locked

- 6. Opcode Menu Configuration Register (OPMENU)

- Entire register is locked

# SPI Lockdown Summary 1

- Locking down the SPI Flash is a little more complicated than locking down SMM

- For the most part, only the vendor can do this, but you can verify and try to implement some yourself

- Verify that BIOS\_CNTL.BLE is set

- Oh wait...we're going to talk about something in a sec that completely bypasses BLE :)

- If it's not set, you can assert it yourself but that doesn't mean there is SMI handler code present that will de-assert bit 0

- Verify that SMM is protecting the BIOS from writes by asserting bit 0 and ensuring that it is reset

- If supported, ensure that BIOS\_CNTL.SMM\_BWP is asserted so that the BIOS can only be written to when the processor is in SMM

- You can set this yourself. The only drawback being that you may not be able to update the BIOS, depending on how the vendor implemented updates

# SPI Lockdown Summary 2

- Verify that Protected Range registers are being used

- You could also set these yourself but it will be a trial and error exercise since you won't know what parts of the BIOS flash will be used to store variables (UEFI definitely and some Legacy)

- Set FLOCKDN to ensure the above registers can't be changed

- The above changes you could play with won't permanently hurt your system if they lock it up – they will all reset back to their original values on startup

- Verify that the Flash Master permissions are set and that the Flash Descriptor region cannot itself be written to

- You have no control over this unless it is writeable, in which case the most you should do is make the FD un-writeable

- Messing with this one could brick your system "permanently"

# SPI Summary

- Locking down the SPI flash memory is the first line of defense against an attacker

- It is complicated and hard for vendors to get right

- It gets a little more complex in UEFI where the SPI flash is specifically used as a file system for storing system variables

- Can't just set a single PR to write-protect the whole BIOS region

- Remember:

- The BIOS boots from the flash and is responsible for configuring all of the settings we have been discussing so far in the class

- Letting an attacker modify the BIOS means game over

- It's not easy, but it's not that hard either for an attacker to modify your BIOS flash

# SPI Summary

- All the settings in this section apply to both x86 and x64 architecture

- All the settings in this section apply to both legacy BIOS and UEFI BIOS

- All the settings in this section apply to systems running legacy MCH/ICH chipsets and the new PCH chipsets

- Except where otherwise noted (SMM\_BWP)